## Product Features

Operating Frequency: 0.1GHz ~ 20GHz

Gain: 17.4dB@10GHz

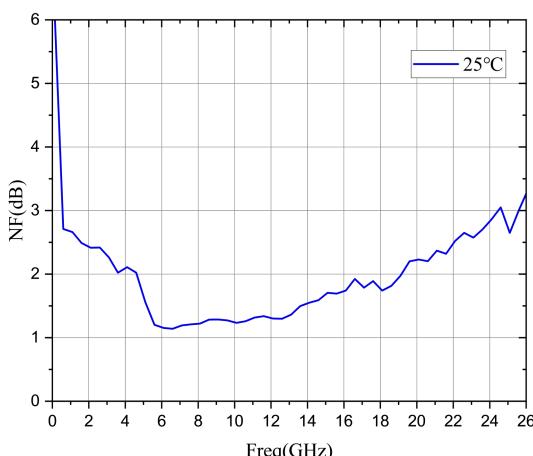

Noise Figure: 1.2dB@10GHz

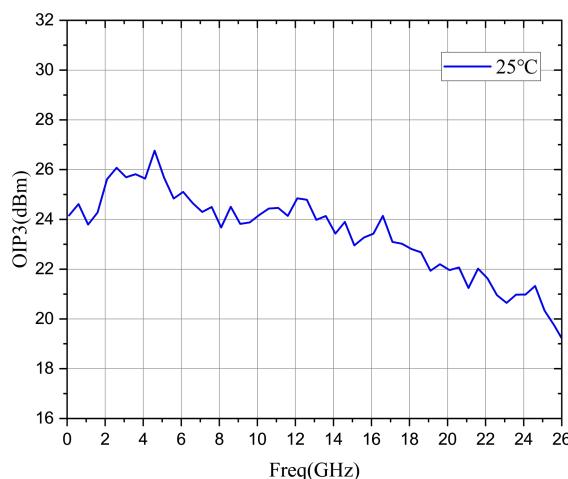

Output Third-Order Interception:

24.2dBm@10GHz

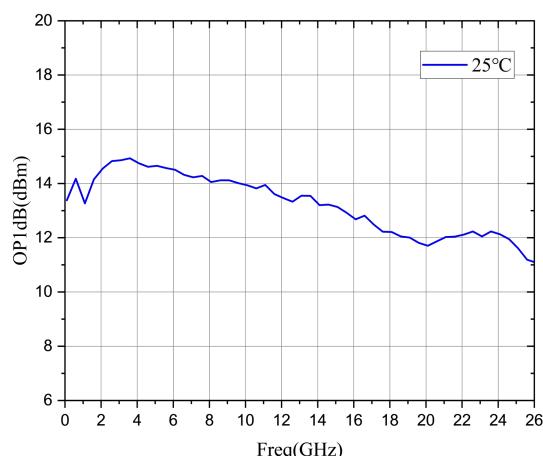

Output Power for 1dB Compression:

13.9dBm@10GHz

Supply Current: 48.5mA @ Vdd=+5V

Chip Size: 3.1 x 1.3 x 0.1(mm)

## Application

Radar and Electronic Countermeasures

Military and Aerospace

Test Instrumentation

## General Description

The BR9615LD is a MMIC gain block amplifier die designed using GaAs process which operates between 0.1GHz and 20GHz. At 10GHz, the amplifier typically provides a gain of 17.4dB, a output P1dB of 13.9dBm, and a noise figure of 1.2dB under the condition of +5V power supply. It has been internally matched to 50 ohms, only requiring blocking capacitors for RF input and output ports. The BR9615LD amplifier is ideal for integration into Multi-Chip-Modules (MCMs) due to its small size.

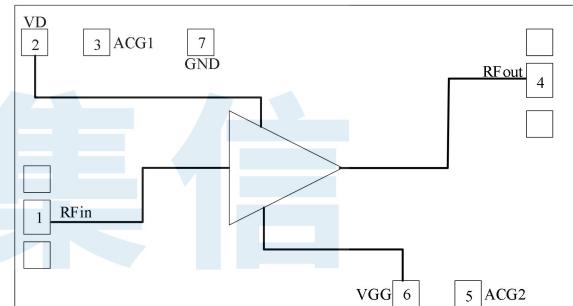

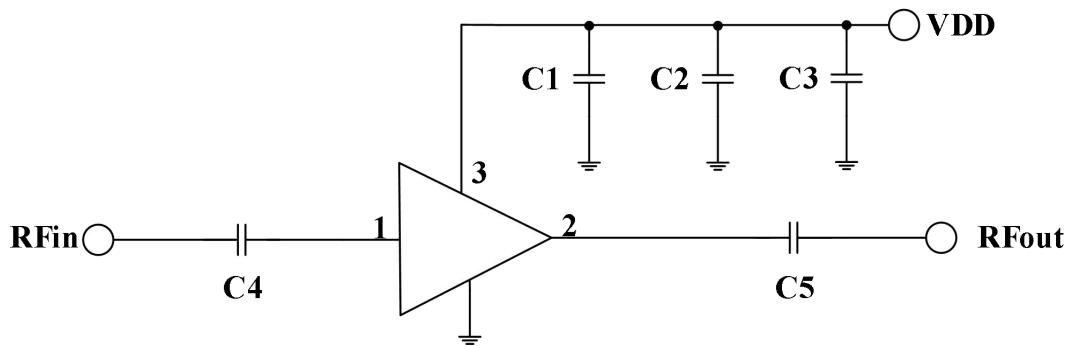

## Functional Block Diagram

## Electrical Specifications

| Parameters                       | Test Condition | Min. | Typ.  | Max. | Units |

|----------------------------------|----------------|------|-------|------|-------|

| Gain                             | 0.1 GHz        | -    | 20.4  | -    | dB    |

|                                  | 10GHz          | -    | 17.4  | -    | dB    |

|                                  | 20GHz          | -    | 17.4  | -    | dB    |

| Output Power for 1dB Compression | 0.1 GHz        | -    | 13.4  | -    | dBm   |

|                                  | 10GHz          | -    | 13.9  | -    | dBm   |

|                                  | 20GHz          | -    | 11.7  | -    | dBm   |

| Output Third-Order Interception  | 0.1 GHz        | -    | 24.1  | -    | dBm   |

|                                  | 10GHz          | -    | 24.2  | -    | dBm   |

|                                  | 20GHz          | -    | 22.0  | -    | dBm   |

| Noise Figure                     | 0.1 GHz        | -    | 6.3   | -    | dB    |

|                                  | 10GHz          | -    | 1.2   | -    | dB    |

|                                  | 20GHz          | -    | 2.2   | -    | dB    |

| Input Return Loss                | 0.1 GHz        | -    | -5.6  | -    | dB    |

|                                  | 10GHz          | -    | -11.2 | -    | dB    |

|                                  | 20GHz          | -    | -21.5 | -    | dB    |

| Output Return Loss               | 0.1 GHz        | -    | -16.3 | -    | dB    |

|                                  | 10GHz          | -    | -32.4 | -    | dB    |

|                                  | 20GHz          | -    | -16   | -    | dB    |

| Supply Voltage                   | -              | -    | 5     | -    | V     |

| Quiescent Current                | -              | -    | 48.5  | -    | mA    |

Test Conditions: VDD=+5V, I=48.5mA, OIP3 spacing=1MHz, Pout=0dBm/tone, TA=+25°C

**Absolute Maximum Ratings**

Maximum Operating Voltage: +5.5V

Maximum RF input Power: +15dBm

**Recommended Operating Conditions**

Supply Voltage: +5V

Supply Current: 48.5mA

Operating Temperature: -55°C ~ +125°C

Storage Temperature: -65°C ~ +150°C

Note: Operation of the device outside the parameter ranges given absolute-maximum-ratings conditions may cause permanent damage, and exposure to absolute-maximum-ratings conditions for extended periods will affect the reliability.

**ESD WARNING**

ELECTROSTATIC SENSITIVE DEVICE

OBSERVE HANDLING PRECAUTIONS

博瑞集信

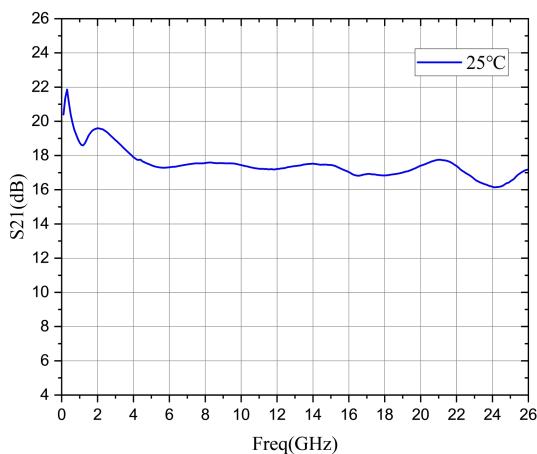

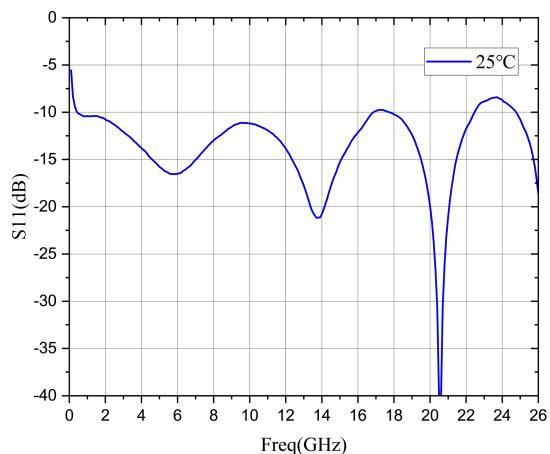

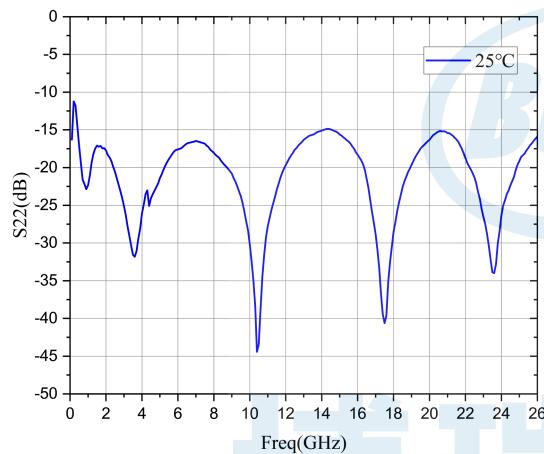

## Typical Performance (VDD=+5V, TA=+25°C)

Gain

Input Return Loss

Output Return Loss

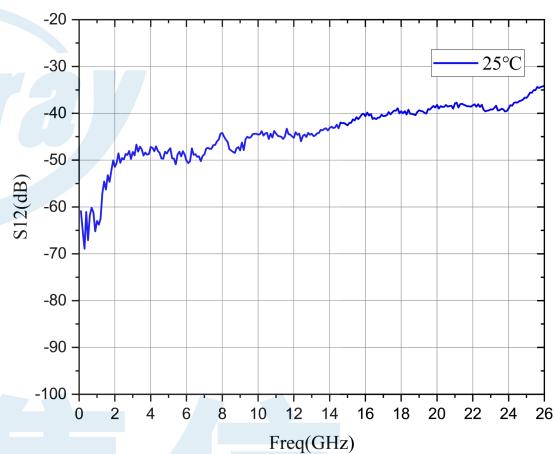

Reverse Isolation

Noise Figure

Output Power for 1dB Compression

**Output Third-Order Interception**

博瑞集信

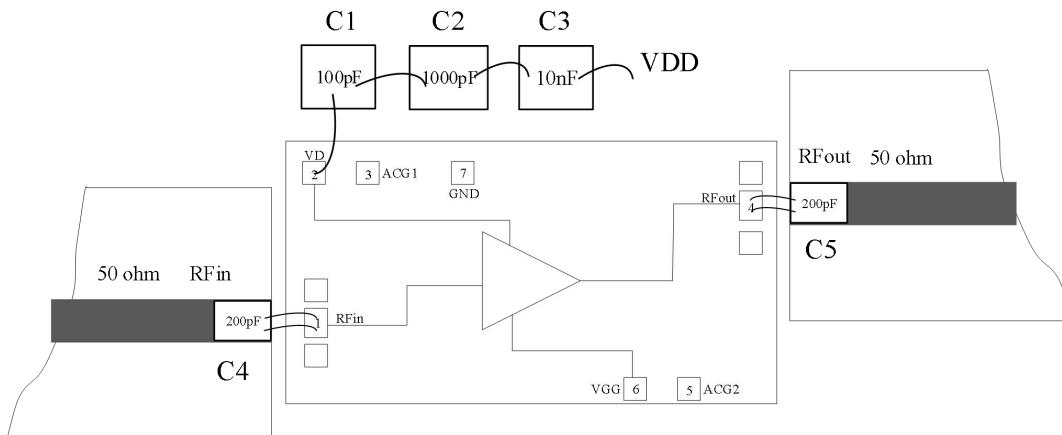

## Typical Application Schematic

## Bill of Material

| Designator | Package        | Description | Part Number             |

|------------|----------------|-------------|-------------------------|

| C1         | Chip Capacitor | 100pF       | SG201N101MSTW           |

| C4、C5      | Chip Capacitor | 200pF       | SG202X201MSTW           |

| C2         | Chip Capacitor | 1000pF      | CT91202X102M100TW       |

| C3         | Chip Capacitor | 10nF        | CT91-20-2X-103-M-50-C-W |

博瑞集信

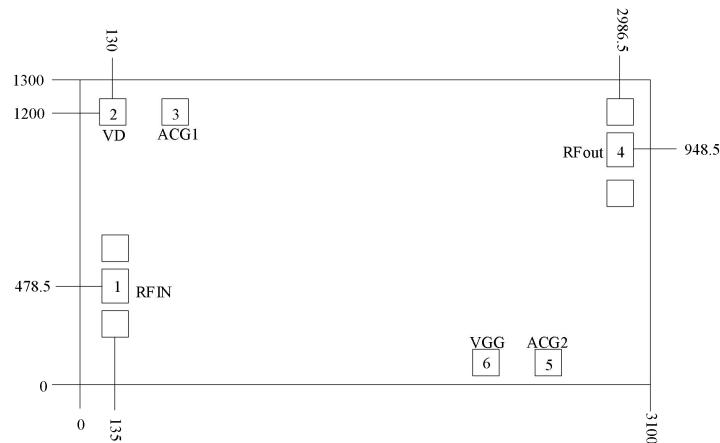

## Assembly Diagram

## Handling Precautions:

- Storage:** All bare die are placed in ESD protective containers, and then sealed in an ESD protective bag for shipment. Once the sealed ESD protective bag has been opened, all die should be stored in a dry nitrogen environment.

- Cleanliness:** Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems.

- Electrostatic protection:** Follow ESD precautions to protect against ESD strikes

- General Handling:** Handle the chip along the edges with a vacuum collet or with a sharp pair of bent tweezers. The surface of the chip should not be touched with vacuum collet, tweezers, or fingers.

- Mouning:** The chip is back-metallized and can be die mounted with AuSn eutectic preforms or with electrically conductive epoxy. The mounting surface should be clean and flat.

- Eutectic Die Attach:** A 80/20 gold tin preform is recommended with a work surface temperature of 255 °C and a tool temperature of 265 °C. When hot 90/10 nitrogen/hydrogen gas is applied, tool tip temperature should be 290 °C. DO NOT expose the chip to a temperature greater than 320 °C for more than 20 seconds. No more than 3 seconds of scrubbing should be required for attachment

- Conductive epoxy Die Attach:** Apply conductive epoxy to the mounting surface so that the overflow of conductive epoxy on all four sides should not be less than 75%, and the height of conductive epoxy climbing on all four sides should not exceed the surface of the chip. Cure conductive epoxy per the manufacturer's schedule.

- Die bonding process unless otherwise noted:** Ball or wedge bond with 0.025mm (1 mil) diameter pure gold wire. Thermosonic wirebonding with a nominal stage temperature of 150 °C is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds. Wirebonds should be started on the chip and terminated on the package or substrate.

- If you have any questions, please contact customer service.

## Mechanical Information (Units: mm)

## Notes:

1. Backside and bond pad metal: Gold

2. Backside is RF and DC ground

3. Pad size: RFin 100um×125um; RFout 100um×125um; VDD 100um×100um;

4. Cannot be bonded on the hole;

| Pad   | Description                                                                                  |

|-------|----------------------------------------------------------------------------------------------|

| RFin  | RF Input, matched to 50 Ohms and DC coupled. See assembly for required external components.  |

| RFout | RF Output, matched to 50 Ohms and DC coupled. See assembly for required external components. |

| VDD   | Power Supply. See assembly for required external components.                                 |

| GND   | Connected to DC/RF ground.                                                                   |